Le differenze fondamentali tra la logica CMOS e TTL includono componenti CMOS più costosi, i circuiti CMOS non assorbono più energia e il consumo di energia TTL aumenta più lentamente. Altre differenze includono la trasmissione di segnali digitali e danni suscettibilità.

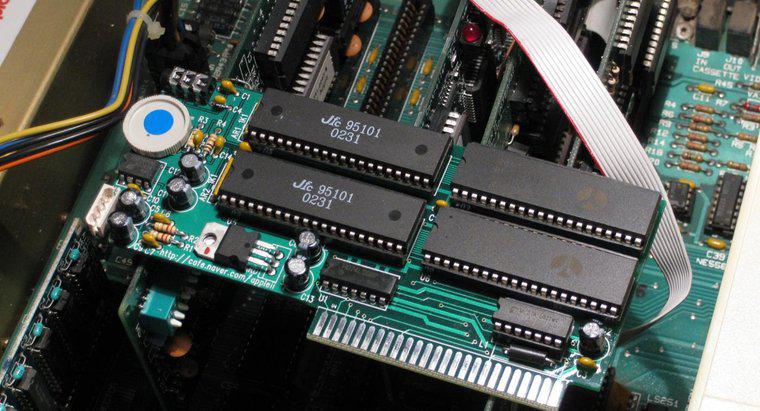

I componenti TTL sono generalmente meno costosi dei componenti CMOS. Tuttavia, a causa di chip più piccoli, CMOS è generalmente meno costoso a livello di sistema. A riposo, i circuiti CMOS non assorbono la stessa potenza dei circuiti TTL. Tuttavia, velocità di clock più elevate fanno aumentare il consumo di energia CMOS a una velocità superiore rispetto a TTL. I componenti CMOS hanno maggiori probabilità di essere danneggiati dalle scariche elettrostatiche rispetto ai componenti TTL. I segnali digitali sono più economici e più semplici con i chip CMOS a causa di tempi di salita e discesa più lunghi.

La dissipazione di potenza del CMOS è generalmente di 10 nW per gate mentre la dissipazione di potenza del TTL è tipicamente di 10 mW per gate. I ritardi di propagazione del TTL sono generalmente di 10 nS mentre i ritardi di propagazione del CMOS sono generalmente compresi tra 25 nS e 50 nS.

L'intervallo del livello di tensione per TTL è generalmente 4,75 V - 5,25 V. L'intervallo del livello di tensione per CMOS varia da 0 a 1/3 VDD a un livello basso e da 2/3 VDD a VDD a un livello alto.